基于 FPGA 的10G 万兆 TCP 协议栈实现 – 服务器版本

概述

在现代网络通信中,万兆网已经成为了高速数据传输的关键组成部分。尤其是在高性能计算、数据中心、工业自动化等领域,万兆网络不仅能够提供极高的带宽,同时也能处理大规模并发的数据流量。为了充分利用这些硬件资源,开发一款高效、低延迟且具有可移植性的万兆 TCP 协议栈成为了很多技术工程师的迫切需求。

本方案基于 FPGA 开发的 万兆 TCP 协议栈实现,使用的硬件平台为 K7325t 开发板,VHDL 纯代码实现,无需 IP 核,便于移植和优化。这一协议栈适合技术工程师、学生以及有需求的开发者用于快速集成、学习和实验。

代码已公开,感兴趣的朋友可以联系我获取源代码。

基于FPGA的10G万兆网TCP/IP 协议栈,服务器版本,纯VHDL代码编写,提供2套工程源码和技术支持

1. 方案介绍

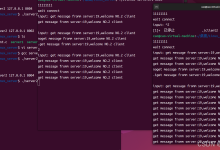

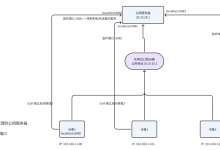

本项目的目标是通过 Xilinx K7 FPGA 实现一个 万兆TCP/IP 协议栈,在此基础上实现测速功能。利用 FPGA 强大的并行计算能力,减少软件协议栈的性能瓶颈,从而实现高吞吐量的数据传输。

该协议栈支持多种 Internet 协议,这些组件可以根据用户应用的需求轻松启用或禁用,包括:

- TCP 服务器:支持多个并发 TCP 连接,数量可在 VHDL 合成前根据 FPGA 资源进行调整。

- UDP 发送/接收:支持 UDP 数据包的发送和接收。

- ARP 和 NDP:支持地址解析协议(ARP)和邻居发现协议(NDP),用于 IP 地址到 MAC 地址的解析。

- PING:支持 ICMP 回显请求和响应,用于网络诊断。

- IGMP:支持多播组管理,适用于多播 UDP 应用。

- DHCP 服务器和客户端:支持动态 IP 地址分配和获取。

- 代码可移植到多种 FPGA 平台,支持 156.25 MHz 的时钟频率。

2. 项目背景

2.1 网络带宽与低延迟需求的日益增加

随着全球数据量的激增以及技术的不断发展,对数据传输速度和实时性的需求也在不断提升。从大数据处理到云计算,再到智能制造和自动驾驶,所有这些应用都依赖于高速网络传输来实现数据的快速交换和实时处理。为了满足这一需求,万兆以太网(10Gbps)作为一种高速网络解决方案,已经成为数据中心、企业网络、超级计算机以及高频交易等领域的标准配置。

然而,虽然万兆以太网提供了超高的传输带宽,但如何高效利用这项技术仍然面临一些挑战。传统的 TCP/IP 协议栈,在面对如此高带宽、高并发的网络环境时,往往会成为性能瓶颈。这不仅限制了数据传输的最大吞吐量,也带来了高延迟和丢包率的问题,严重影响了网络应用的效率和稳定性。

2.2 FPGA 的优势:硬件加速协议栈

FPGA(现场可编程门阵列),作为一种硬件可编程的计算平台,凭借其高度的并行计算能力和低延迟的特点,成为了解决这一问题的理想选择。与传统的软件协议栈不同,FPGA 可以将 TCP/IP 协议栈 中的各个功能模块直接硬件化,实现数据包的高速处理和传输,从而显著降低延迟,提升吞吐量。

通过将协议栈的处理过程从软件转移到硬件,FPGA 可以直接与网络接口卡(NIC)进行交互,避免了传统 TCP 协议栈中的上下文切换和 CPU 负载。FPGA 能够以并行的方式处理大量数据流,支持多个并发连接,同时还可以根据需要灵活配置协议栈的各个模块,达到定制化的需求。

此外,FPGA 提供了极高的灵活性,用户可以根据实际需求对协议栈进行优化和修改,例如调整 TCP 拥塞控制策略、调整数据包大小、优化内存访问等。这使得 FPGA 成为一种非常适合高吞吐量、低延迟网络应用的硬件平台。

2.3 万兆 TCP 协议栈的市场需求

目前,很多高性能网络应用都需要 万兆网络协议栈,尤其是在数据中心、云计算、超级计算、金融高频交易和大规模实时数据传输的场景中,低延迟和高吞吐量是决定系统性能的关键。因此,如何在万兆网络环境中提供一个高效、稳定、可扩展的 TCP 协议栈,成为了技术工程师和网络架构师的紧迫需求。

传统的基于 CPU 的协议栈无法满足这些要求,而基于 FPGA 的硬件加速协议栈则为解决这一问题提供了有效的方案。与软件协议栈相比,基于 FPGA 的协议栈具有以下显著优势:

- 低延迟:FPGA 可以直接处理数据包,无需通过操作系统内核,减少了软件协议栈中的上下文切换和中断处理,从而显著降低了网络通信的延迟。

- 高吞吐量:通过硬件加速,FPGA 能够处理更高带宽的数据流,达到比软件协议栈更高的吞吐量。

- 低 CPU 占用:由于数据包的处理任务被移交给 FPGA,CPU 可以腾出更多资源,处理其他任务,提高系统的整体效率。

- 高并发支持:FPGA 通过并行处理,能够支持更多的并发连接,解决传统协议栈在高并发连接下的瓶颈问题。

2.4 项目背景的创新点

本项目的创新之处在于 完全基于 VHDL 编写的万兆 TCP 协议栈,完全避免了 IP 核的使用,确保了协议栈的可定制性和移植性。这一协议栈不仅支持 K7325t 开发板,也可移植到其他 FPGA 开发平台上,具有广泛的应用前景。

通过这套 万兆 TCP 协议栈,用户不仅能够在硬件层面加

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册